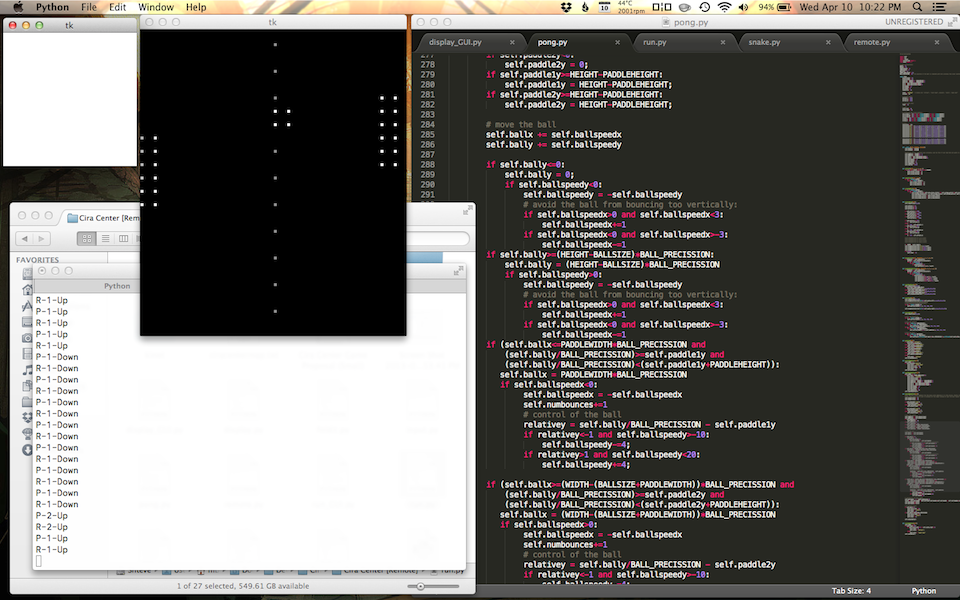

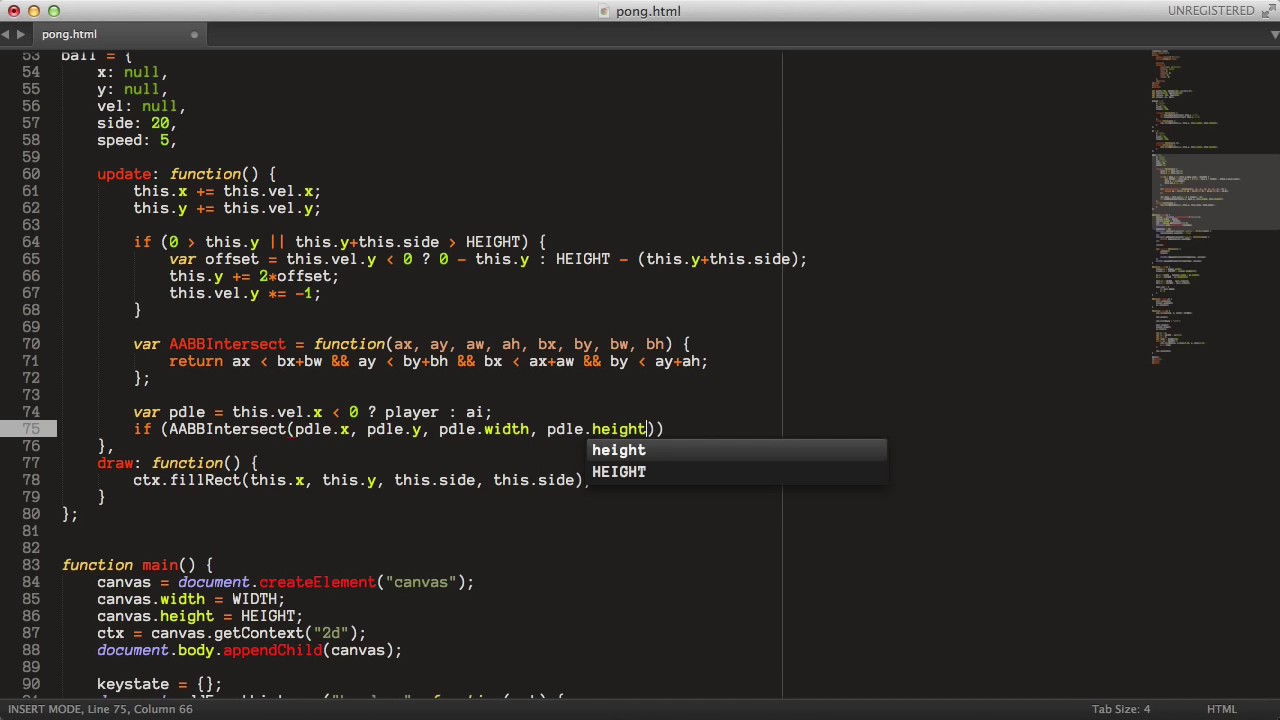

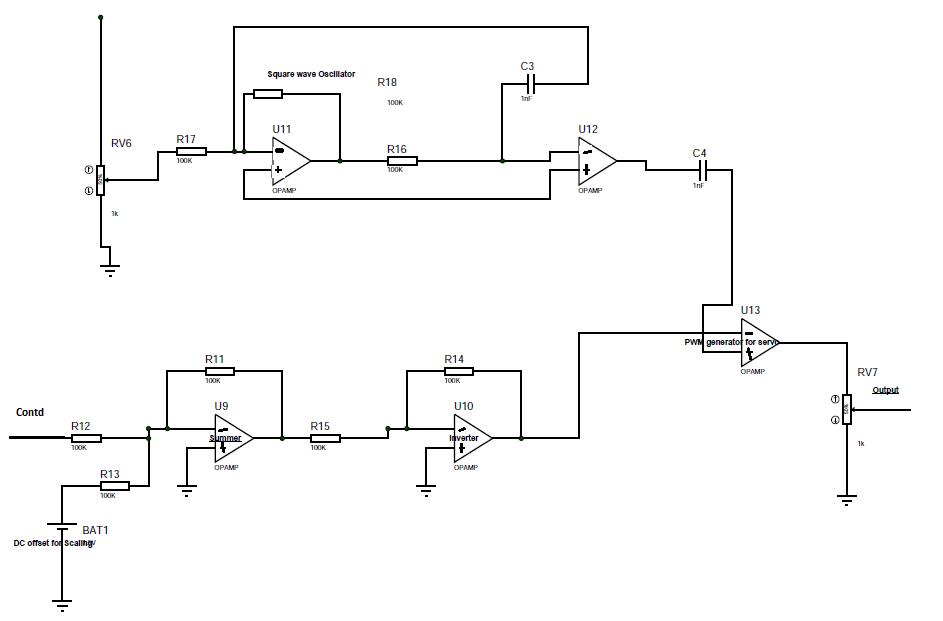

The first component is the one where registers are defined, the second one contains our code. To make the AXI peripheral IP, write you code in vhdl, then select AXI peripheral when you want to package your IP.Īxi peripheral has two components. The first address is written and others are shifted by 4, because 32 bits width data bus are used. The second way is packing our code as AXI peripheral, where we can decide how many register we are going to use.Īdresses can be seen in address editor above block diagram. Although it is a fast and simple solution, I would need to use a lot of them to communicate with all my ports. Two disadvantages of this solution are, that it uses a lot of resources, and that it only has two ports. The first one is general purpose interface, AXI_GPIO.

To connect SDK application and hardware designed in Vivado there needs to be some registers reserved through which the data can be send and received from. Pong game code in vhdl series#They are in a series connection, and the last component sends the united RGB signal to the screen.ītn_RE IP is there for capturing the signals from the buttons and rotary encoder from the extern board. Two Table IPs add the first and the second racket.

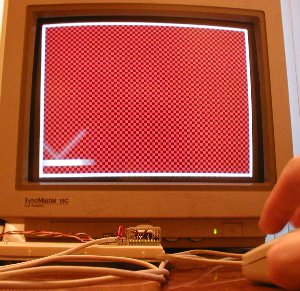

PP_ball is the first in the row, and it draws the ball and score bar. Each of those three generates their part of the picture. VGA IP sends the coordinates to PP_ball, Table and Table IP.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed